Descripción

The MC10EL/100EL32 is an integrated divide by 2 divider. The differential clock inputs and the VBB allow a differential, single-ended or AC coupled interface to the device. If used, the VBB output should be bypassed to ground with a 0.01 F capacitor. Also note that the VBB is designed to be used as an input bias on the EL32 only, the VBB output has limited current sink and source capability. The reset pin is asynchronous and is asserted on the rising edge. Upon power-up, the internal flip-flop will attain a random state, the reset allows for the synchronization of multiple EL32’s in a system. The 100 Series contains temperature compensation.

510ps Propagation Delay

3.0GHz Toggle Frequency

ESD Protection: > 1 KV HBM, > 100 V MM

PECL Mode Operating Range: VCC= 4.2 V to 5.7 V with VEE= 0 V

NECL Mode Operating Range: VCC= 0 V with VEE= -4.2 V to -5.7 V

Internal Input Pulldown Resistors on CLK(s) and R.

Moisture Sensitivity Level 1

Transistor Count = 82 devices

Applications

Phase Lock Loops

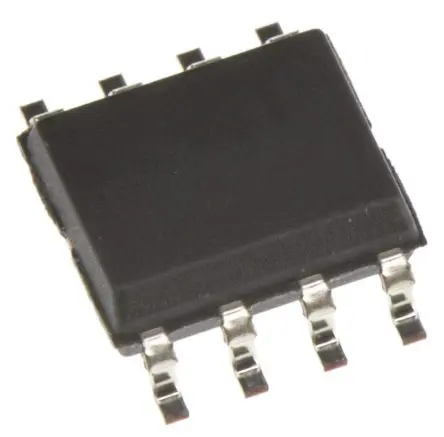

| Atributo | Valor |

|---|---|

| Familia Lógica | ECL |

| Función Lógica | Divisor |

| Número de Elementos por Chip | 2 |

| Tipo de Montaje | Montaje superficial |

| Tipo de Encapsulado | SOIC |

| Conteo de Pines | 8 |

| Dimensiones | 5 x 4 x 1.5mm |

| Altura | 1.5mm |

| Longitud | 5mm |

| Tensión de Alimentación Máxima de Funcionamiento | 5.7 V |

| Ancho | 4mm |

| Tensión de Alimentación de Funcionamiento Mínima | 4.2 V |

| Temperatura de Funcionamiento Mínima | -40 °C |

| Temperatura Máxima de Funcionamiento | +85 °C |

Valoraciones

No hay valoraciones aún.